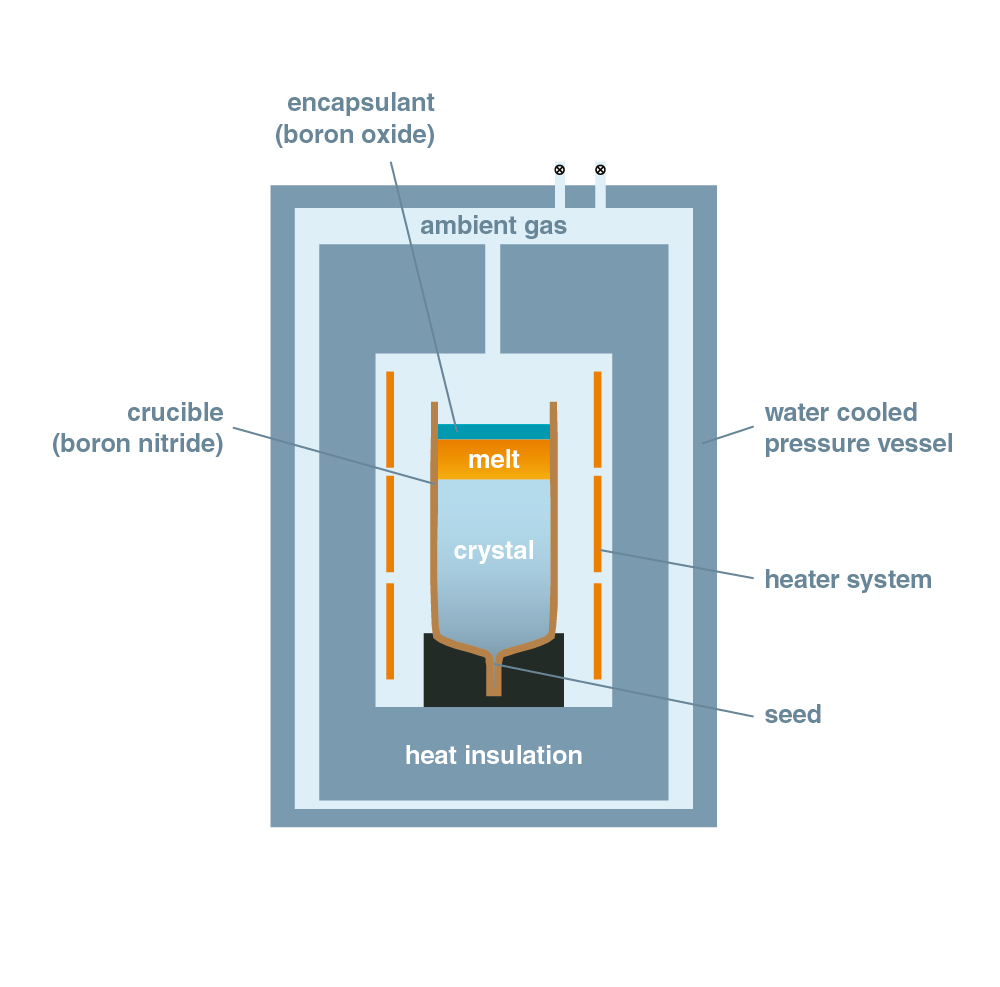

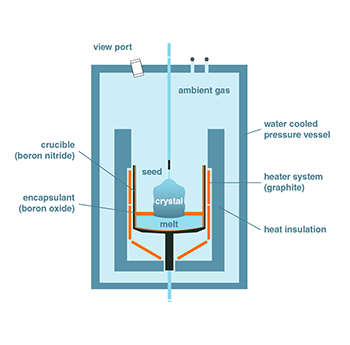

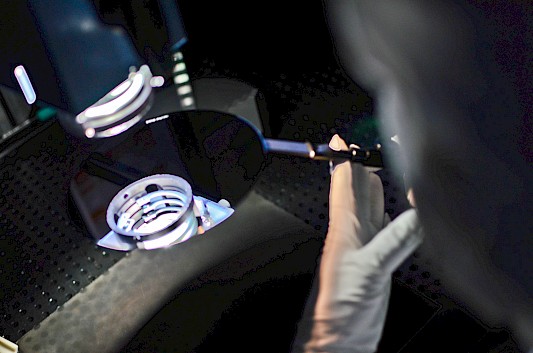

Crystal growth is initiated mostly by a <100>-oriented seed fixed in the lower part of the crucible and continued with an upward moving solid/liquid interface.

The temperature field is moved by a proper control of the heater system ensuring the given growth rate and interface shape. The low axial temperature gradient of typically below 5K/cm leads to crystals characterized by very low dislocation density.